The question as stated has some serious issues:

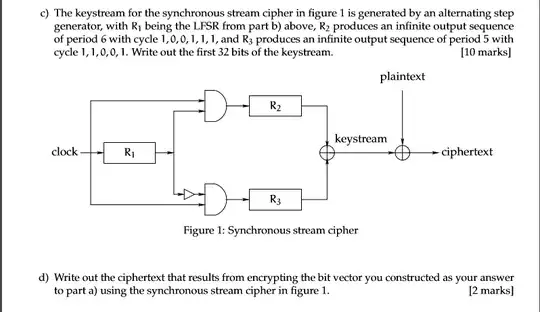

The alternating step generator works with 3 LFSRs. If the output of R1 is 1, then R3 is clocked, otherwise R2 is clocked, so at each clock period exactly one of those two is clocked. The output of R2 and R3 is added modulo 2 to form the keystream. The initial loadings of the 3 LFSRs is essentially the key.

The example in the question is quite strange. The LFSRs should be maximum length (i.e., primitive). You can have a primmitive LFSR of cycle length 7, e.g., and instead nonprimitive LFSR with cycle lengths 5 and 6 are used--this would have statistical properties worse than a primitive LFSR and lead to problems.

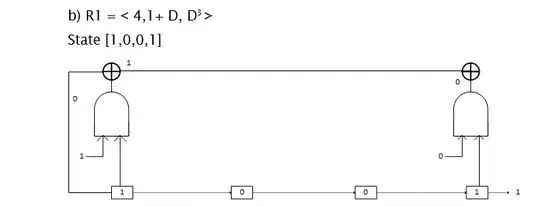

Even ignoring this, the nonstandard notation $<4, 1+D, D^3>$ is used for R1. I have no idea what this means.

In particular, in the figure from part (b), a constant bit of $0$ is AND'ed to one of the registers which might as well be removed, since the output is always zero! Thus, the LFSR is defective in that it is only sampling two bits, and not at the two ends.